#### **♦ IO-**Link SLAVE TRANSCEIVER

Rev B2, Page 1/38

#### **FEATURES**

- ♦ IO-Link COM3-compliant slave transceiver (230.4 kBaud)

- ♦ Dual-channel switches, configurable for high-side, low-side and push-pull operation with tristate function

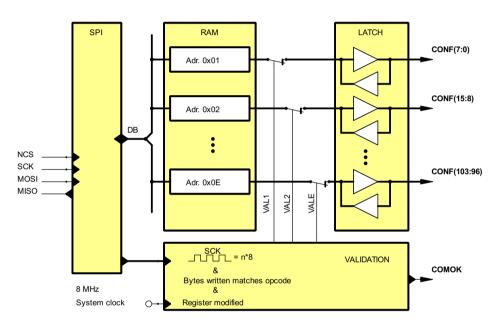

- ♦ Configuration via SPI interface with secured data transmission

- ♦ Switches are programmable current limited

- Switches, iC supply and feedback channel are protected against reverse polarity

- ♦ Output current of up to 200 mA per channel

- ♦ Parallel connection of both channels possible

- ♦ The channels can be inverted for antivalent output

- ♦ Sensor communication request function (*IO-Link wake-up*)

- ♦ Wide supply voltage range of 4.5 to 36 V

- ♦ Sensor parametrization via two feedback channels (up to 36 V)

- ♦ Switching converter and linear regulators with 5/3.3/2.5/1.8 V output voltage

- ♦ On-chip digital temperature sensor with alarm

- IRQ output with excess temperature, overload and under-voltage

- ♦ Driver shut-down on errors

#### **APPLICATIONS**

- ♦ IO-Link slaves

- ♦ I/O sensor interface

- ♦ Digital sensors

- ♦ Proximity switches

- Light barriers

#### **PACKAGES**

QFN24 4 mm x 4 mm (RoHS compliant)

#### **IO-Link SLAVE TRANSCEIVER**

Rev B2, Page 2/38

#### **DESCRIPTION**

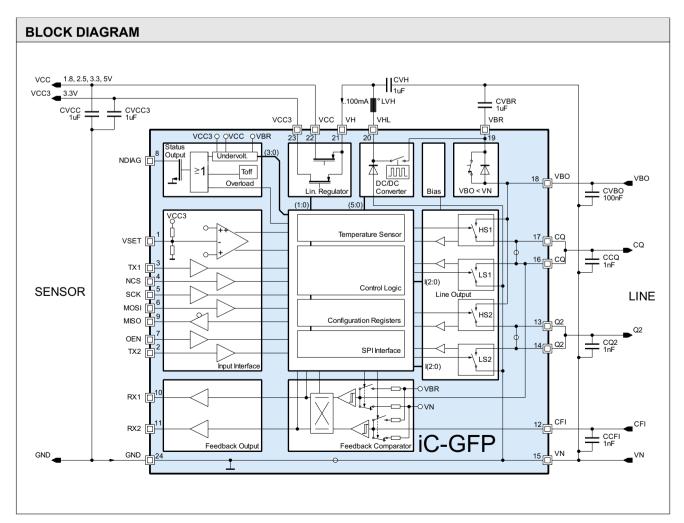

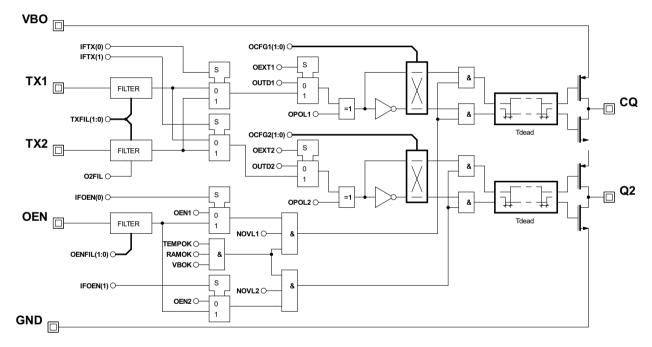

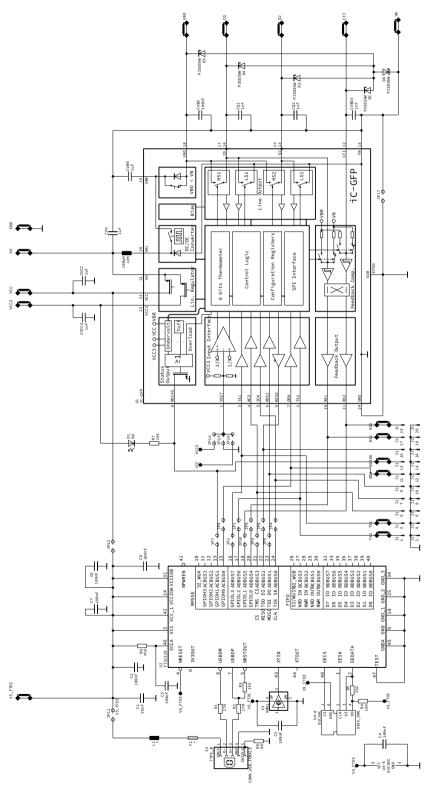

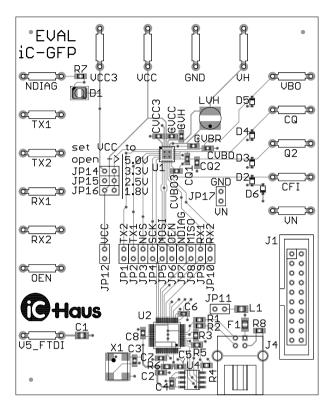

iC-GFP is a fully IO-Link COM3-compliant transceiver iC with two independent switching channels which enables digital sensors to drive peripheral elements, such as programmable logic controllers (PLC) and relays, for example.

The outputs can be configured for push-pull, high-side or low-side operation. A synchronized mode permits both channels to work as one or in antivalent mode. The switches are designed to cope with high driver currents of up to 200 mA, are current limited, and also short-circuit-proof in that they shut down with excessive temperature or overload. The output current limit is set digitally via SPI.

The overload protection is accomplished in a way so that capacitive loads can be switched with low repeat rates without the protective circuitry cutting in. In the event of excess temperature an error message is generated immediately.

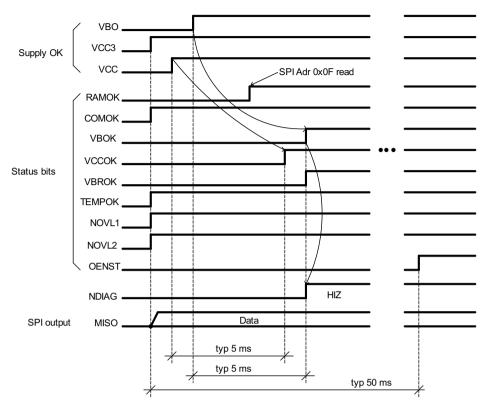

The iC-GFP performs a self-diagnostic function and signals errors at the open-collector output, NDIAG. The outputs are shut down in case of errors.

To avoid error signalling during power-up, the outputs remain at high impedance for ca. 50 ms.

The chip acts as an SPI slave and allows function configuration via secured register access. It also features

diagnostic registers and supports *communication requests* (= IO-Link *wake-up*) at pin CFI or CQ which generate interrupt signals at pin NDIAG.

The pins on the 24 V line side of the sensor interface (VBO, CQ, Q2, VN, and CFI) are protected against reverse polarity. This makes any external reverse polarity protection diodes superfluous.

iC-GFP features an integrated switching converter which generates voltages VCC (5, 3.3, 2.5, 1.8 V, selectable) and VCC3 (3.3 V) with the aid of two downstream linear regulators. For *medium* currents the inductor may as well be replaced by a resistor (e.g.  $170\,\Omega$ ), resulting though in a considerably less efficiency. If only a low current is required inductor LVH may be omitted completely; the linear regulators are then powered directly by VBR.

The switching regulator comes equipped with a spread-spectrum oscillator to reduce interferences.

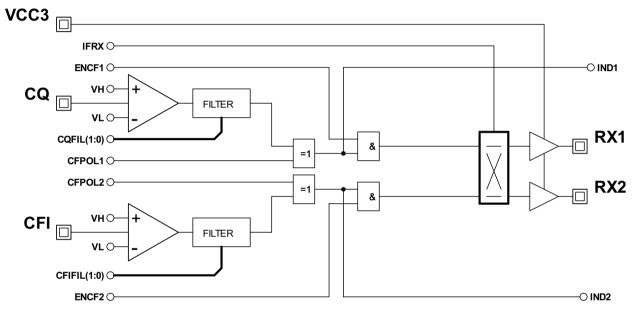

The connected sensor can be parametrised using the feedback channels (CFI/CQ  $\rightarrow$  RX1/RX2).

A digital temperature sensor provides the chip temperature, readable by the MCU. A programmable temperature alarm is provided as well.

Rev B2, Page 3/38

#### **PACKAGING INFORMATION**

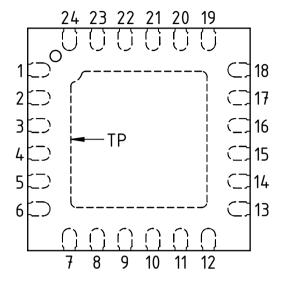

#### PIN CONFIGURATION QFN24 4 mm x 4 mm

#### **PIN FUNCTIONS**

| No. | Name  | Function                             |

|-----|-------|--------------------------------------|

| 1   | VSET  | Voltage Configuration for VCC        |

| 2   | TX2   | Input Channel 2                      |

| 3   | TX1   | Input Channel 1                      |

| 4   | NCS   | Chip Select                          |

| 5   | SCK   | SPI Serial Clock                     |

| 6   | MOSI  | Master Output Slave Input            |

| 7   | OEN   | Output Enable Input                  |

| 8   | NDIAG | Diagnostics Output                   |

| 9   | MISO  | Master Input Slave Output            |

| 10  | RX1   | Feedback Output 1                    |

| 11  | RX2   | Feedback Output 2                    |

| 12  | CFI   | Feedback Channel Input               |

| 13  | Q2    | Output Channel 2                     |

| 14  | Q2    | Output Channel 2                     |

| 15  | VN    | Ground                               |

| 16  | CQ    | I/O Channel                          |

| 17  | CQ    | I/O Channel                          |

| 18  | VBO   | Power Supply                         |

| 19  | VBR   | Power Supply for switching converter |

| 20  | VHL   | Switching Converter Inductance       |

| 21  | VH    | Input Linear Regulators              |

|     | VCC   | 5/3.3/2.5/1.8 V Sensor Supply        |

| 23  | VCC3  | 3.3 V Sensor Supply                  |

| 24  | GND   | Sensor Ground                        |

|     | TP    | Thermal Pad                          |

The Thermal Pad is to be connected to a Ground Plane (VN) on the PCB.

Only pin 1 marking on top or bottom defines the package orientation (iC-GFP label and coding is subject to change).

Rev B2, Page 4/38

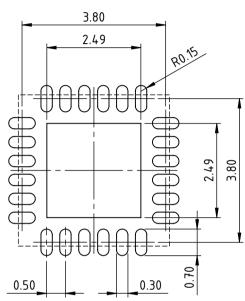

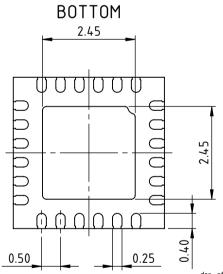

#### PACKAGE DIMENSIONS QFN24 4 mm x 4 mm

All dimensions given in mm.

# SIDE

### RECOMMENDED PCB-FOOTPRINT

dra\_qfn24-1\_pack\_1, 10:1

Rev B2, Page 5/38

#### **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed. Absolute Maximum Ratings are no operating conditions! Integrated circuits with system interfaces, e.g. via cable accessible pins (I/O pins, line drivers) are per principle endangered by injected interferences, which may compromise the function or durability. The robustness of the devices has to be verified by the user during system development with regards to applying standards and ensured where necessary by additional protective circuitry. By the manufacturer suggested protective circuitry is for information only and given without responsibility and has to be verified within the actual system with respect to actual interferences.

| Item<br>No. | Symbol  | Parameter                                                               | Conditions                                                                                                                                      | Min.        | Max.      | Unit     |

|-------------|---------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|----------|

| G001        | VBO     | Power Supply at VBO                                                     | Referenced to lowest voltage of VN, VBR, CQ, Q2, CFI, VH, VHL Referenced to highest voltage of VN, VBR, CQ, Q2, CFI, VH, VHL                    | -36         | 36        | V        |

| G002        | I(VBO)  | Current in VBO                                                          | Q2, 51 1, 111, 1112                                                                                                                             | -10         | 600       | mA       |

| G003        |         | Voltage at VBR                                                          | Referenced to lowest voltage of VN, VBO, CQ,                                                                                                    |             | 36        | V        |

|             |         |                                                                         | Q2, CFI, VH, VHL Referenced to highest voltage of VN, VBO, CQ, Q2, CFI, VH, VHL                                                                 | -36         |           | V        |

| G004        | I(VBR)  | Current in VBR                                                          |                                                                                                                                                 | -600        | 150       | mA       |

| G005        | V(VH)   | Voltage at VH                                                           | Referenced to lowest voltage of VN, VBR,<br>VBO, CQ, Q2, CFI, VHL<br>Referenced to highest voltage of VN, VBR,<br>VBO, CQ, Q2, CFI, VHL         | -36         | 36        | V        |

| G006        | I(V/H)  | Current in VH                                                           | VBO, CQ, QZ, OI I, VIIL                                                                                                                         | -5          | 120       | mA       |

|             | V(VHL)  | Voltage at VHL                                                          | Referenced to lowest voltage of VN, VBR,                                                                                                        | -5          | 36        | V        |

| 0007        | V(VIIL) | voltage at viil                                                         | VBO, CQ, Q2, CFI, VH Referenced to highest voltage of VN, VBR, VBO, CQ, Q2, CFI, VH                                                             | -36         |           | V        |

| G008        | I(VHL)  | Current in VHL                                                          |                                                                                                                                                 | -150        | 5         | mA       |

| G009        | V(VN)   | Voltage at VN vs. GND                                                   |                                                                                                                                                 | -0.5        | 0.5       | V        |

| G010        | I(VN)   | Current in VN                                                           | VN < VBO<br>VN > VBO                                                                                                                            | -500<br>-10 | 500<br>10 | mA<br>mA |

| G011        | V()     | Voltage at VCC, VCC3                                                    |                                                                                                                                                 | -0.3        | 7         | V        |

| G012        | I()     | Current in VCC, VCC3                                                    |                                                                                                                                                 | -50         | 10        | mA       |

| G013        | V()     | Voltage at CQ, Q2                                                       | Referenced to lowest voltage of VN, VBO,<br>VBR, CQ, Q2, CFI, VH, VHL<br>Referenced to highest voltage of VN, VBO,<br>VBR, CQ, Q2, CFI, VH, VHL | -36         | 36        | V        |

| G014        | I()     | Current in CQ, Q2                                                       |                                                                                                                                                 | -400        | 400       | mA       |

| G015        | V(CFI)  | Voltage at CFI                                                          | Referenced to lowest voltage of VN, VBO, VBR, CQ, Q2, VH, VHL                                                                                   |             | 36        | V        |

|             |         |                                                                         | Referenced to highest voltage of VN, VBO, VBR, CQ, Q2, VH, VHL                                                                                  | -36         |           | V        |

| G016        | I(CFI)  | Current in CFI                                                          |                                                                                                                                                 | -4          | 4         | mA       |

| G017        | V()     | Voltage at MOSI, SCK, NCS, TX1, TX2<br>VSET, OEN, RX1, RX2, NDIAG, MISO | ,                                                                                                                                               | -0.3        | 7         | V        |

| G018        | I()     | Current in MOSI, SCK, NCS, TX1, TX2, VSET, OEN                          | ,                                                                                                                                               | -4          | 4         | mA       |

| G019        | I()     | Current in RX1, RX2, MISO                                               |                                                                                                                                                 | -70         | 70        | mA       |

| G020        | I()     | Current in NDIAG                                                        |                                                                                                                                                 | -4          | 70        | mA       |

| G021        | Vd()    | ESD Susceptibility at all pins                                          | HBM, 100 pF discharged through 1.5 kΩ                                                                                                           |             | 2         | kV       |

| G022        | Tj      | Junction Temperature                                                    |                                                                                                                                                 | -40         | 150       | °C       |

| G023        | Ts      | Storage Temperature Range                                               |                                                                                                                                                 | -40         | 150       | °C       |

Rev B2, Page 6/38

#### THERMAL DATA

| Item | Symbol | Parameter                                                       | Conditions                                                   |      |      |      | Unit |

|------|--------|-----------------------------------------------------------------|--------------------------------------------------------------|------|------|------|------|

| No.  |        |                                                                 |                                                              | Min. | Тур. | Max. |      |

| T01  |        | Operating Ambient Temperature Range (extended range on request) |                                                              | -40  |      | 85   | °C   |

| T02  | Rthja  |                                                                 | Surface mounted, thermal pad soldered to ca. 2 cm² heat sink |      | 30   | 40   | K/W  |

Rev B2, Page 7/38

#### **ELECTRICAL CHARACTERISTICS**

| ltem<br>No. | Symbol      | Parameter                                                                                                                | Conditions                                                                                                           | Min.                                 | Тур. | Max.                                   | Unit                       |

|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|----------------------------------------|----------------------------|

| Total       | Device      |                                                                                                                          |                                                                                                                      |                                      |      |                                        |                            |

| 001         | VBO         | Permissible Supply Voltage                                                                                               | Referenced to VN                                                                                                     | 4.5                                  | 24   | 36                                     | V                          |

| 002         | I(VBO)      | Supply Current in VBO                                                                                                    | No load, VH conected to VBR, I(CQ) = I(Q2) = 0, CQ/Q2 switched on                                                    |                                      |      | 5.5                                    | mA                         |

| 003         | Vs(VBR)     | Saturation Voltage at VBR                                                                                                | Vs(VBR) = V(VBO) — V(VBR);<br>I(VBR) = -20 mA<br>I(VBR) = -50 mA                                                     |                                      |      | 1<br>1.2                               | V                          |

| 004         | VH          | Permissible Voltage at VH                                                                                                |                                                                                                                      | 5                                    |      | 36                                     | V                          |

| 005         | I(VH)       | Supply Current in VH                                                                                                     | VH = 8 V, no load, I(VCC) = I(VCC3) = 0,<br>V(OEN) = hi                                                              | 0.5                                  |      | 3                                      | mA                         |

| 006         | Vc()hi      | Clamp Voltage hi at VBO, VBR vs. VN                                                                                      | I() = 10 mA                                                                                                          | 36                                   |      |                                        | V                          |

| 007         | Vc()lo      | Clamp Voltage lo at VBO, VBR vs. VN                                                                                      | I() = -10 mA                                                                                                         |                                      |      | -36                                    | V                          |

| 800         | Vc()hi      | Clamp Voltage hi at CQ, Q2 vs. VN                                                                                        | I() = 1 mA, VBO > VN                                                                                                 | 36                                   |      |                                        | V                          |

| 009         | Vc()lo      | Clamp Voltage lo at CQ, Q2 vs. VBO                                                                                       | I() = -1 mA, VBO > VN                                                                                                |                                      |      | -36                                    | V                          |

| 010         | Vc()hi      | Clamp Voltage hi at VN, VBO,<br>VBR, CQ, Q2, CFI, VH, VHL vs.<br>lowest voltage of VN, VBO, VBR,<br>CQ, Q2, CFI, VH, VHL | I() = 1 mA                                                                                                           | 36                                   |      |                                        | V                          |

| 011         | Vc()hi      | Clamp Voltage hi at VSET, RX1, RX2, MISO                                                                                 | I() = 1 mA                                                                                                           | 7                                    |      |                                        | V                          |

| 012         | Vc()lo      | Clamp Voltage Io MOSI, SCK,<br>NCS, TX1, TX2, VSET, OEN,<br>RX1, RX2, NDIAG, MISO, VCC,<br>VCC3, VHL                     | I() = -1 mA                                                                                                          |                                      |      | -0.4                                   | V                          |

| 013         | Vc()lo      | Clamp Voltage lo at VH                                                                                                   | I() = -4 mA                                                                                                          | -1.9                                 |      | -0.4                                   | V                          |

| 014         | RGND        | Resistance GND to VN                                                                                                     |                                                                                                                      |                                      | 3    | 7                                      | Ω                          |

| Low-        | Side Switch | CQ, Q2                                                                                                                   |                                                                                                                      | ·                                    |      |                                        | -                          |

| 101         | Vs()lo      | Saturation Voltage lo at CQ, Q2 vs. VN                                                                                   | OVLCx(2:0) = 101, VBO = 936 V;<br>I() = 200 mA<br>I() = 150 mA<br>I() = 100 mA<br>I() = 50 mA<br>I() = 10 mA         |                                      |      | 1.8<br>1.5<br>1.3<br>0.9<br>0.5        | V<br>V<br>V                |

| 102         | Vs()lo      | Saturation Voltage lo at CQ, Q2 vs. VN                                                                                   | OVLCx(2:0) = 101, VBO = 4.59 V;<br>I() = 150 mA<br>I() = 100 mA<br>I() = 50 mA<br>I() = 10 mA                        |                                      |      | 2.3<br>1.8<br>1.2<br>0.6               | V<br>V<br>V                |

| 103         | Isc()lo     | Short-Circuit Current lo in CQ, Q2                                                                                       | OVLCx(2:0) = 0x0<br>OVLCx(2:0) = 0x1<br>OVLCx(2:0) = 0x2<br>OVLCx(2:0) = 0x3<br>OVLCx(2:0) = 0x4<br>OVLCx(2:0) = 0x5 | 55<br>80<br>110<br>140<br>170<br>210 |      | 120<br>150<br>195<br>230<br>280<br>310 | mA<br>mA<br>mA<br>mA<br>mA |

| 104         | Vol()on     |                                                                                                                          | CQ, Q2 lo $\rightarrow$ hi, referenced to GND                                                                        | 2.2                                  |      | 3.5                                    | V                          |

| 105         | Vol()off    |                                                                                                                          | CQ, Q2 hi $\rightarrow$ lo, referenced to GND                                                                        | 2.1                                  |      | 2.9                                    | V                          |

| 106         | Vol()hys    | Overload Detection Threshold<br>Hysteresis                                                                               | Vol()hys = Vol()on — Vol()off                                                                                        | 0.1                                  |      |                                        | V                          |

| 107         | SR()        | Slew Rate (switch off $\rightarrow$ on)                                                                                  | VBO = 36 V, CI = 2.2 nF, OVLCx(2:0) = 0x5;<br>HSPx = 0; EXCHx = 0<br>HSPx = 1; EXCHx = 1                             | 60                                   |      | 45                                     | V/µs<br>V/µs               |

| 108         | Imax()      | Maximum Current in CQ, Q2                                                                                                | OVLCx(2:0) = 0x7, V() > 3 V, VBO = 936 V                                                                             | 250                                  | 300  | 390                                    | mA                         |

Rev B2, Page 8/38

#### **ELECTRICAL CHARACTERISTICS**

| ltem<br>No. | Symbol      | Parameter                                  | Conditions                                                                                                                                                            | Min.                                         | Тур.       | Max.                                       | Unit                       |

|-------------|-------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------|--------------------------------------------|----------------------------|

| 109         | Ir()        | Reverse Current in CQ, Q2                  | Low side = on, V() = -6 V                                                                                                                                             | -330                                         |            |                                            | μA                         |

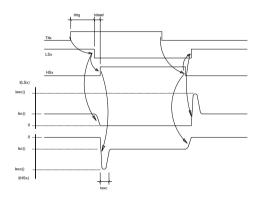

| 110         | lexc()      | Excitation Current                         | EXCx = 1, VBO = 936 V;<br>HSPx = 0 (see Fig. 5)<br>HSPx = 1 (see Fig. 5)                                                                                              | 300                                          |            | 540<br>700                                 | mA<br>mA                   |

| 111         | texc        | Excitation Time                            | EXCx = 1 (see Fig. 5), oscillator calibrated;<br>TEXCx = 0<br>TEXCx = 1                                                                                               | 2.2<br>6.7                                   | 2.5<br>7.5 | 2.7<br>8.1                                 | μs<br>μs                   |

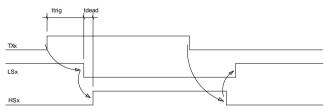

| 112         | tdead       | Dead Time                                  | Push-pull configuration, low switch activation delay after high switch deactivation (see Fig. 4), oscilator calibrated; HSPx = 0 HSPx = 1                             |                                              | 500<br>125 | 540<br>135                                 | ns<br>ns                   |

| 113         | llk()       | Leakage Current at CQ, Q2                  | OEN = Io, EPUCF1 = 0, OVLCx(2:0) = 0x2;<br>V(CQ, Q2) = VBOVBO + 3 V, VBO = 4.533 V<br>V(CQ, Q2) = 0VBO<br>V(CQ, Q2) = -60 V; VBO = 036 V<br>V(CQ, Q2) = VBO - 36 V3 V | 0<br>-70<br>-90<br>-200                      |            | 300<br>70<br>0                             | μΑ<br>μΑ<br>μΑ<br>μΑ       |

| High-       | Side Switch | h CQ, Q2                                   |                                                                                                                                                                       |                                              |            |                                            |                            |

| 201         | Vs()hi      | Saturation Voltage hi vs. VBO              | OVLCx(2:0) = 101, VBO = 936 V;<br>I() = -200 mA<br>I() = -150 mA<br>I() = -100 mA<br>I() = -50 mA<br>I() = -10 mA                                                     | -1.8<br>-1.5<br>-1.3<br>-0.9<br>-0.4         |            |                                            | V<br>V<br>V                |

| 202         | Vs()hi      | Saturation Voltage hi vs. VBO              | OVLCx(2:0) = 101, VBO = 4.59 V;<br>I() = -150 mA<br>I() = -100 mA<br>I() = -50 mA<br>I() = -10 mA                                                                     | -2.3<br>-1.8<br>-1.2<br>-0.6                 |            |                                            | V<br>V<br>V                |

| 203         | Isc()hi     | Short-Circuit Current hi                   | V() = 0 VVBO - 3 V, VBO = 936 V;<br>OVLCx(2:0) = 0x0<br>OVLCx(2:0) = 0x1<br>OVLCx(2:0) = 0x2<br>OVLCx(2:0) = 0x3<br>OVLCx(2:0) = 0x4<br>OVLCx(2:0) = 0x5              | -120<br>-150<br>-195<br>-240<br>-285<br>-330 |            | -55<br>-80<br>-100<br>-140<br>-170<br>-200 | mA<br>mA<br>mA<br>mA<br>mA |

| 204         | Vol()on     | Overload Detection Threshold on            | CQ, Q2 hi $\rightarrow$ lo, referenced to VBO;                                                                                                                        | -3.9                                         |            | -2.5                                       | V                          |

| 205         | Vol()off    | Overload Detection Threshold off           | CQ, Q2 lo $\rightarrow$ hi, referenced to VBO;                                                                                                                        | -3.3                                         |            | -2.1                                       | V                          |

| 206         | Vol()hys    | Overload Detection Threshold<br>Hysteresis | Vol()hys = Vol()off — Vol()on                                                                                                                                         | 0.1                                          |            |                                            | V                          |

| 207         | SR()        | Slew Rate (switch off $\rightarrow$ on)    | VBO = 36 V, CI = 2.2 nF, OVLCx(2:0) = 0x5;<br>HSPx = 0; EXCx = 0<br>HSPx = 1; EXCx = 1                                                                                | 35                                           |            | 40                                         | V/µs<br>V/µs               |

| 208         | lmax()      | Maximum Current in CQ, Q2                  | OVLCx(2:0) = 0x7, V() < VBO - 3 V,<br>VBO = 936 V                                                                                                                     | -650                                         |            | -250                                       | mA                         |

| 209         | lr()        | Reverse Current in CQ, Q2                  | CQ, Q2 on, V() = VBOVBO + 3 V,<br>VBO = 4.533 V                                                                                                                       |                                              |            | 300                                        | μA                         |

| 210         | lexc()      | Excitation Current                         | EXCx = 1, VBO = 936 V;<br>HSPx = 0 (see Fig. 5)<br>HSPx = 1 (see Fig. 5)                                                                                              | -360<br>-700                                 |            | -260                                       | mA<br>mA                   |

| 211         | texc        | Excitation Time                            | EXCx = 1 (see Fig. 5), oscillator calibrated;<br>TEXCx = 0<br>TEXCx = 1                                                                                               | 2.2<br>6.7                                   | 2.5<br>7.5 | 2.7<br>8.1                                 | μs<br>μs                   |

| 212         | tdead       | Dead Time                                  | Push-pull configuration, high switch activation delay after low switch deactivation (see Fig. 4), oscillator calibrated; HSPx = 0 HSPx = 1                            |                                              | 500<br>125 | 540<br>135                                 | ns<br>ns                   |

Rev B2, Page 9/38

#### **ELECTRICAL CHARACTERISTICS**

| ltem<br>No. | Symbol                | Parameter                                                                | Conditions                                                                       | Min.               | Тур.     | Max.             | Unit             |

|-------------|-----------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------|----------|------------------|------------------|

| Short-      | -Circuit/Ove          | rload Monitor/Wake-Up Request                                            |                                                                                  | "                  |          |                  |                  |

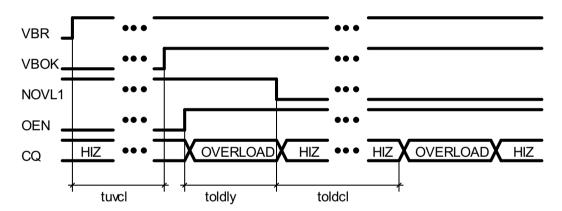

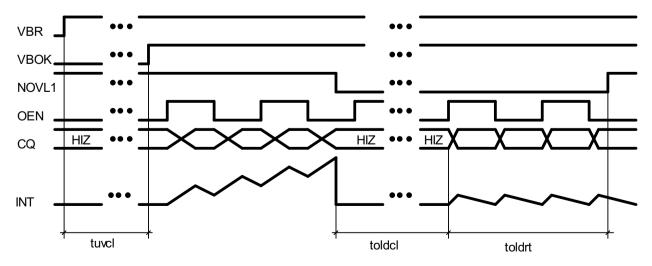

| 301         | toldly                | Time to Overload Message (OVLx 0 → 1, outputs tri-state)                 | Permanent overload (see Fig. 9)                                                  | 126                | 160      | 213              | μs               |

| 302         | tolcl                 | Time to start retry (outputs active)                                     |                                                                                  | 35                 | 50       | 80               | ms               |

| 303         | toldrt                | Time to Overload Message clearing (OVLx 1 $\rightarrow$ 0) during retry  | No overload (see Fig. 10)                                                        |                    | 1        |                  | ms               |

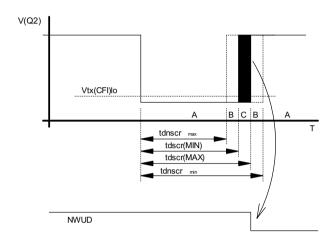

| 304         | tdscr                 | Time to Wake-Up Request acknowledge                                      | OVLCx < 5                                                                        | 73                 |          | 87               | μs               |

| 305         | tdnscr <sub>max</sub> | Maximum Time for no Wake-Up Request decision                             |                                                                                  |                    |          | 40               | μs               |

| 306         | tdnscr <sub>min</sub> | Minimum Time for no Wake-Up Request decision                             |                                                                                  | 125                |          |                  | μs               |

| VBO \       | /oltage Mor           | nitor                                                                    |                                                                                  |                    |          |                  |                  |

| 401         | VBOon                 | Turn-On Threshold VBO                                                    | Referenced to GND;<br>UVTH(3:0) = 0x0<br>UVTH(3:0) = 0x4<br>UVTH(3:0) = 0xF      | 3.5<br>8<br>17.7   |          | 4.5<br>9<br>20   | V<br>V<br>V      |

| 402         | VBOoff                | Turn-Off Threshold VBO                                                   | Decreasing voltage VBO;<br>UVTH(3:0) = 0x0<br>UVTH(3:0) = 0x4<br>UVTH(3:0) = 0xF | 3.5<br>7.3<br>17.5 |          | 4.4<br>8.9<br>20 | V<br>V<br>V      |

| 403         | VBOhys                | Hysteresis                                                               | VBOhys = VBOon - VBOoff                                                          | 50                 | 500      |                  | mV               |

| 404         | tUVB                  | UVBO flag persistence after event                                        | No undervoltage at VBO                                                           |                    | 5        |                  | ms               |

| 405         | tUVBFIL               | VBO undervoltage detection filtering time                                | UVFIL = '0'<br>UVFIL = '1'                                                       |                    | 0.1<br>1 |                  | ms<br>ms         |

| 406         | Vt()VNBR              | NVBREV flag, autarchy monitor threshold, activated                       | VBR referenced to VBO                                                            | 0.1                |          | 2                | V                |

| 407         | tVNBRFIL              | Required event duration before setting VNBREV                            |                                                                                  |                    | 10       |                  | μs               |

| 408         | tVNBR                 | NVBREV flag persistence after event                                      | VBR – VBO > VNBRth                                                               |                    | 5        |                  | ms               |

| 409         | Ir(VBR)               | Reverse Supply current from VBR to VBO                                   | VBR – VBO > 1V                                                                   |                    |          | 0.5              | mA               |

| 410         | C(VBR)                | Maximum Capacitance at VBR                                               |                                                                                  |                    | 100      |                  | μF               |

|             | erature Mor           |                                                                          |                                                                                  |                    |          |                  |                  |

| 501         | Toff                  | Overtemperature Shutdown (TEMPOK 1 $\rightarrow$ 0, switch tri-state)    | Increasing temperature Tj                                                        | 140                |          | 175              | °C               |

| 502         | ton                   | Overtemperature Shutdown<br>Reset Delay<br>(TEMPOK 0 → 1, switch active) | Temperature Tj < Toff                                                            | 35                 | 50       | 80               | ms               |

| 503         | Trange                | Temperature Digital Measure-<br>ment Range                               |                                                                                  | -40                |          | 125              | °C               |

| 504         | Tresol                | Temperature Digital Measure-<br>ment Resolution                          |                                                                                  |                    | 1        |                  | °C               |

| 505         | Reading               | Temperature Value Ranges                                                 | Tj = 125 °C<br>Tj = -40 °C                                                       | 170<br>5           |          | 195<br>25        | digits<br>digits |

| Inputs      | TX1, TX2,             | MOSI, NCS, SCK, OEN                                                      |                                                                                  |                    |          |                  |                  |

| 601         | Vt()hi                | Input Threshold Voltage hi at TX1, TX2, MOSI, SCLK, OEN, NCS             |                                                                                  |                    |          | 1.7              | V                |

| 602         | Vt()lo                | Input Threshold Voltage Io at TX1, TX2, MOSI, SCK, OEN, NCS              |                                                                                  | 0.8                |          |                  | V                |

Rev B2, Page 10/38

#### **ELECTRICAL CHARACTERISTICS**

| ltem<br>No. | Symbol             | Parameter                                              | Conditions                                                                         | Min.         | Тур. | Max.        | Unit                     |

|-------------|--------------------|--------------------------------------------------------|------------------------------------------------------------------------------------|--------------|------|-------------|--------------------------|

| 603         | Vt()hys            | Hysteresis at TX1, TX2, MOSI, SCK, OEN, NCS            | Vt()hys = Vt()hi - Vt()lo                                                          | 20           | 140  |             | mV                       |

| 604         | lpd()              | Pull-Down Current at TX1, TX2, MOSI, SCK               | V() = 0.4 VVCC3                                                                    | 2            |      | 40          | μA                       |

| 605         | Rpu()              | Pull-up resistor at NCS                                | NCS to VCC3                                                                        |              | 100  |             | kΩ                       |

| 606         | lpd(OEN)           | Pull-Down Current at OEN                               | V(OEN) = 0.4 VVCC3                                                                 | 1            |      | 6           | μA                       |

| 607         | tspu()             | Permissible Spurious Pulse<br>Width at TX1, TX2        | No activity triggered, TXFIL(1:0) = 10                                             |              |      | 2.5         | μs                       |

| 608         | ttrig()            | Required Pulse Width at TX1, TX2                       | Activity triggered, TXFIL(1:0) = 10                                                | 6            |      |             | μs                       |

| 609         | tspu()             | Permissible Spurious Pulse<br>Width at OEN             | No activity triggered, OENFIL(1:0) = 10                                            |              |      | 5           | μs                       |

| 610         | ttrig()            | Required Pulse Width at OEN                            | Activity triggered, OENFIL(1:0) = 10                                               | 12           |      |             | μs                       |

| 611         | tpio               | $    \begin{array}{l}                                $ | TXFIL(1:0) = 10                                                                    | 2.4          |      | 10          | μs                       |

| Diag (      | Output NDIA        | AG and MISO                                            |                                                                                    |              |      |             |                          |

| 701         | Vs()lo             | Saturation Voltage lo at MISO, NDIAG                   | I() = 1.0 mA                                                                       |              |      | 0.4         | V                        |

| 702         | llk()              | Leakage Current in MISO                                | V() = 0 VVCC, NCS = hi                                                             | -10          |      | 10          | μA                       |

| 703         | llk()              | Leakage Current in NDIAG                               | V() = 0 VVCC, no error                                                             | -10          |      | 10          | μA                       |

| 704         | Vs()hi             | Saturation Voltage high at MISO                        | I(MISO) = -2 mA,<br>Vs(MISO)hi = VCC3 — V(MISO)                                    |              |      | 0.4         | V                        |

| 705         | Isc()hi            | Short Circuit current hi in MISO                       | V(MISO) = 0VCC3 - 0.4 V                                                            | -100         |      |             | mA                       |

| 706         | lsc()lo            | Short Circuit current lo in MISO                       | V(MISO) = 0.4 VVCC3                                                                |              |      | 100         | mA                       |

| 707         | lsc()lo            | Short Circuit current lo in NDIAG                      | V(NDIAG) = 0.4 VVCC3                                                               |              |      | 15          | mA                       |

| 708         | tr(MISO)           | Rise Time                                              | CI(MISO) = 30 pF, 0 → 90% VCC3                                                     |              |      | 6           | ns                       |

| 709         | tf(MISO)           | Fall Time                                              | 100 → 10% VCC3                                                                     |              |      | 6           | ns                       |

| Feedb       | ack Channe         | el CQ, CFI to RX1, RX2                                 |                                                                                    |              |      |             |                          |

| 801         | Vt1()hi            | Input Threshold 1 hi at CQ, CFI                        | VBO < 18 V                                                                         | 59           | 66   | 74          | %VBR                     |

| 802         | Vt1()lo            | Input Threshold 1 lo at CQ, CFI                        | VBO < 18 V                                                                         | 44           | 50   | 56          | %VBR                     |

| 803         | Vt2()hi            | Input Threshold 2 hi at CQ, CFI                        | VBO > 18 V                                                                         | 10.5         | 11.3 | 12.5        | V                        |

| 804         | Vt2()lo            | Input Threshold 2 lo at CQ, CFI                        | VBO > 18 V                                                                         | 8.3          | 9    | 10.5        | V                        |

| 805         | Vt()hys            | Hysteresis at CQ, CFI                                  | Vt()hys = Vt()hi - Vt()lo                                                          | 1            |      |             | V                        |

| 806         | lpu()              | Pull-Up Current at CQ, CFI                             | EPUCFx = 1, PUNPDx = 1,<br>V(CQ, CFI) = 0VBO - 3 V;<br>VBO = 4.59 V<br>VBO = 936 V | -370<br>-370 |      | -80<br>-120 | μ <b>Α</b><br>μ <b>Α</b> |

| 807         | lpd()              | Pull-Down Current at CQ, CFI                           | EPUCFx = 1, PUNPDx = 0,<br>V(CQ,CFI) = 3 VVBO;<br>VBO = 4.59 V<br>VBO = 936 V      | 80<br>120    |      | 370<br>370  | μΑ<br>μΑ                 |

| 808         | tpcf               | Propagation Delay<br>CQ, CFI → RX1, RX2                | V(RX1,RX2) = 10 ↔ 90%, RXFIL(1:0) = 01                                             | 2.4          |      | 10          | μs                       |

| 809         | tsup()             | Permissible Spurious Pulse<br>Width at CQ,CFI          | No activity triggered, RXFIL(1:0) = 01                                             |              |      | 2.5         | μs                       |

| 810         | ttrig()            | Required Pulse Width at CQ, CFI                        | Activity triggered, RXFIL(1:0) = 01                                                | 6            |      |             | μs                       |

| 811         | lpd(C)+<br>llk(Q2) | Pull-Down Current at CFI plus leakage current at Q2    | V() = 3 VVBO, OEN = Io, PUNPD2 = 0,<br>EPUCF2 = 1                                  | 20           |      |             | μA                       |

| 812         | Vs()hi             | Saturation Voltage hi at RX1, RX2                      | I() = -2 mA, Vs()hi = VCC3 - V()                                                   |              |      | 0.4         | V                        |

| 813         | Vs()lo             | Saturation Voltage low at RX1, RX2                     | I() = 2 mA                                                                         |              |      | 0.4         | V                        |

Rev B2, Page 11/38

#### **ELECTRICAL CHARACTERISTICS**

| Item<br>No. | Symbol     | Parameter                                                    | Conditions                                                                                                                                                                                                                                                 | Min.                     | Тур.                   | Max.                     | Unit                             |

|-------------|------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|--------------------------|----------------------------------|

| 814         | Isc()hi    | Short Circuit current hi in RX1, RX2                         | V() = 0VCC3 - 0.4 V                                                                                                                                                                                                                                        | -40                      |                        |                          | mA                               |

| 815         | Isc()lo    | Short Circuit current lo in RX1, RX2                         | V() = 0.4 VVCC3                                                                                                                                                                                                                                            |                          |                        | 90                       | mA                               |

| 816         | tr()       | Rise Time at RX1, RX2                                        | CL() = 30 pF, 0 → 90% VCC3                                                                                                                                                                                                                                 |                          |                        | 22                       | ns                               |

| 817         | tf()       | Fall Time at RX1, RX2                                        | CL() = 30 pF, 100 → 10% VCC3                                                                                                                                                                                                                               |                          |                        | 22                       | ns                               |

| Step [      | Down Conve | erter VHL, VH                                                |                                                                                                                                                                                                                                                            |                          |                        |                          |                                  |

| 901         | I(VH)max   | Maximum current in VH                                        | LVH = 100 μH, Ri(LVH) < 1.1 $\Omega$ , CVH = 10 μF; VHV(5:0) = 0x040x17 VHV(5:0) = 0x180x2C                                                                                                                                                                |                          |                        | 100<br>70                | mA<br>mA                         |

| 902         | VHstep     | VH configuration steps                                       | Register VHV(5:0)                                                                                                                                                                                                                                          |                          | 250                    |                          | mV                               |

| 905         | VHn        | Nominal Voltage at VH                                        | LVH = $100 \mu\text{H}$ , Ri(LVH) < $1.1 \Omega$ , CVH = $10 \mu\text{F}$ ; VBO > $10 \text{V}$ ; VHV(5:0) = $0x04$ , II = $0100 \text{mA}$ VHV(5:0) = $0x0B$ , II = $0100 \text{mA}$ VBO > (VH + $4 \text{V}$ ); VHV(5:0) = $0x18$ , II = $070 \text{mA}$ | 4.7<br>6.3<br>9.5        | 5<br>6.75              | 5.4<br>7.5<br>10.5       | V                                |

|             |            |                                                              | VHV(5:0) = 0x2C, II = 070 mA                                                                                                                                                                                                                               | 14.3                     | 15                     | 15.6                     | V                                |

| 906         | VHnr       | Nominal Voltage at VH, LVH replaced by a resistor            | R = 170 Ω, I(VH) = 010 mA, VBO > 10 V,<br>VHV(5:0) = 0x0B                                                                                                                                                                                                  | 6.3                      |                        | 8.4                      | V                                |

| 907         | la(VHL)    | max. DC Cut-Off Current in VHL                               |                                                                                                                                                                                                                                                            | -400                     |                        | -120                     | mA                               |

| 908         | Va(VH)     | Cut-Off Voltage at VH                                        | Va(VH) > VHn; VHV(5:0) = 0x0B                                                                                                                                                                                                                              | 6.5                      | 7.3                    | 8.4                      | V                                |

| 910         | Vs(VHL)    | Saturation Voltage at VHL vs. VBR                            | I(VHL) = -50 mA<br>I(VHL) = -150 mA                                                                                                                                                                                                                        |                          | 0.5<br>1.5             | 1.1<br>3.0               | V                                |

| 911         | Vf(VHL)    | Saturation Voltage at VHL vs. GND                            | Vf(VHL) = V(GND) — V(VHL);<br>I(VHL) = -50 mA<br>I(VHL) = -150 mA                                                                                                                                                                                          |                          | 0.6<br>1.7             | 1.5<br>2.9               | V                                |

| 912         | llk(VHL)   | Leakage Current at VHL                                       | VHL = Io, V(VHL) = V(VH)                                                                                                                                                                                                                                   | -20                      |                        | 20                       | μA                               |

| 913         | $\eta$ VH  | Efficiency of VH switching regulator                         | I(VH) = 50 mA, Ri(LVH) < 1.1 $\Omega$ ,<br>V(VBR) = 1236 V                                                                                                                                                                                                 | 70*                      |                        |                          | %                                |

| Series      | Regulator  | vcc                                                          |                                                                                                                                                                                                                                                            |                          |                        |                          |                                  |

| A01         | VCCn       | Nominal Voltage at VCC                                       | I(VCC) = -500 mA, VH = VHn;<br>VSET open, VH > 6.3 V<br>VSET tied to VCC3<br>VSET tied to GND<br>VSET tied to VCC                                                                                                                                          | 4.5<br>3.0<br>2.3<br>1.6 | 5<br>3.3<br>2.5<br>1.8 | 5.5<br>3.6<br>2.7<br>2.0 | V<br>V<br>V                      |

| A02         | VCCdrop    | Minimum voltage drop<br>VH – VCC                             | EVCC = 1, VSET = open;<br>I(VCC) = -10 mA<br>I(VCC) = -50 mA                                                                                                                                                                                               | 0.75<br>1.25             |                        |                          | V                                |

| A03         | CVCC       | Required Capacitor at VCC vs. GND                            |                                                                                                                                                                                                                                                            | 150                      |                        |                          | nF                               |

| A04         | RiCVCC     | Maximum Permissible Internal Resisitance of capacitor at VCC |                                                                                                                                                                                                                                                            |                          |                        | 1                        | Ω                                |

| A05         | VCCon      | VCC Monitor Threshold hi                                     | Increasing Voltage at VCC;<br>VSET open<br>VSET tied to VCC3<br>VSET tied to GND<br>VSET tied to VCC                                                                                                                                                       | 70<br>70<br>60<br>50     |                        | 98<br>98<br>98<br>98     | %VCCn<br>%VCCn<br>%VCCn<br>%VCCn |

| A06         | VCCoff     | VCC Monitor Threshold Io                                     | Decreasing Voltage at VCC;<br>VSET open<br>VSET tied to VCC3<br>VSET tied to GND<br>VSET tied to VCC                                                                                                                                                       | 70<br>70<br>60<br>50     |                        | 95<br>95<br>95<br>95     | %VCCn<br>%VCCn<br>%VCCn<br>%VCCn |

| A07         | VCChys     | Hysteresis                                                   | VCChys = VCCon — VCCoff                                                                                                                                                                                                                                    | 20                       | 400                    |                          | mV                               |

| A08         | tUVCCFIL   | VCC undervoltage detection filtering time                    | Continuous VCC undervoltage                                                                                                                                                                                                                                |                          | 30                     |                          | μs                               |

<sup>\*</sup> Projected values by sample characterization

Rev B2, Page 12/38

#### **ELECTRICAL CHARACTERISTICS**

| ltem   | Symbol      | Parameter                                                     | Conditions                                          |          |      |      | Unit |

|--------|-------------|---------------------------------------------------------------|-----------------------------------------------------|----------|------|------|------|

| No.    |             |                                                               |                                                     | Min.     | Тур. | Max. |      |

| A09    | tUVCC       | UVCC flag persistence after event                             | No undervoltage at VCC                              |          | 5    |      | ms   |

| Series | s Regulator | VCC3                                                          |                                                     |          |      |      |      |

| B01    | VCC3n       | Nominal Voltage at VCC3                                       | I(VCC3) = -500 mA, VH = VHn                         | 3.0      | 3.3  | 3.6  | V    |

| B02    | CVCC3       | Required Capacitor at VCC3 vs. GND                            |                                                     | 150      |      |      | nF   |

| B03    | VCC3drop    | Minimum voltage drop<br>VH - VCC3                             | I(VCC3) = 0 mA<br>I(VCC3) = -50 mA                  | 0.4<br>1 |      |      | V    |

| B04    | RiCVCC3     | Maximum Permissible Internal Resisitance of capacitor at VCC3 |                                                     |          |      | 1    | Ω    |

| B05    | VCC3on      | VCC3 Monitor Threshold hi                                     | Increasing Voltage at VCC3                          | 2.3      |      | 3.0  | V    |

| B06    | VCC3off     | VCC3 Monitor Threshold lo                                     | Decreasing Voltage at VCC3                          | 2.0      |      | 2.8  | V    |

| B07    | VCC3hys     | Hysteresis                                                    | VCC3hys = VCC3on — VCC3off                          | 50       | 450  |      | mV   |

| Oscill | ator        |                                                               |                                                     |          |      | ,    |      |

| C01    | fos         | Oscillator Frequency                                          |                                                     | 7.35     | 8    | 8.83 | MHz  |

| SPI in | terface     |                                                               |                                                     |          |      | ,    |      |

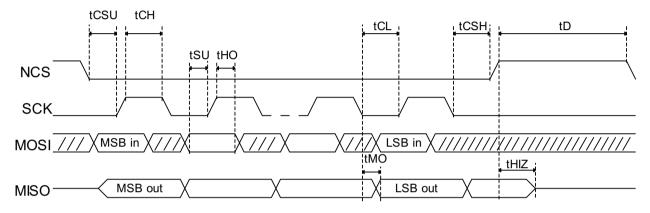

| E01    | tCSU        | Chip select setup time                                        | NCS stable low prior to SCLK rising edge            | 30       |      |      | ns   |

| E02    | tCSH        | Chip select hold time                                         | NCS stable low after last SCLK falling edge         | 30       |      |      | ns   |

| E03    | tCH         | SCLK clock high time                                          |                                                     | 31       |      |      | ns   |

| E04    | tCL         | SCLK clock low time                                           |                                                     | 31       |      |      | ns   |

| E05    | tSU         | MOSI to clock setup time                                      | MOSI stable before SCLK rising edge                 | 4        |      |      | ns   |

| E06    | tHO         | MOSI to clock hold time                                       | MOSI stabla after SCLK rising edge                  | 15       |      |      | ns   |

| E07    | tD          | NCS high time                                                 | NCS stable at high after SPI communication          | 180      |      |      | ns   |

| E08    | tMO         | MISO valid time                                               | MISO valid after SCLK falling edge, CI $\leq$ 30 pF | 0        |      | 25   | ns   |

| E09    | tHIZ        | MISO to HIZ time                                              | MISO set to high impedance after NCS rising edge    |          |      | 160  | ns   |

| E10    | fSCLK       | SPI clock frequency                                           |                                                     |          |      | 16   | MHz  |

#### **IO-Link SLAVE TRANSCEIVER**

Rev B2, Page 13/38

#### **DESCRIPTION OF FUNCTIONS**

iC-GFP has two independent switching channels which enable digital sensors to drive peripheral elements. They are designed to cope with high driver currents. The switches are reverse-polarity protected, feature a free-wheeling circuit for inductive loads and a saturation-voltage minimising system.

#### Reverse polarity protection

The pins VBO, CQ, Q2, VN, and CFI on the *line side* of the chip are reverse polarity protected. As far as the maximum voltage ratings are not exceeded, no possible supply combination at the *line side* pins can damage the chip.

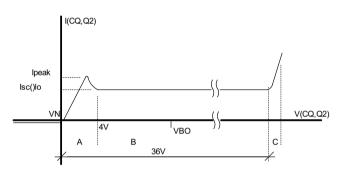

Figure 1: Low-side switch characteristic when active

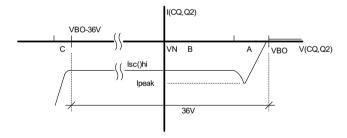

Figure 2: High-side switch characteristic when active

#### Output characteristics of CQ, Q2

The switching channels are current limited to a value set by the OVLCx bits. The current limitation works only for voltages higher than 4 V at the low-side switches or lower than VBO - 4 V at the high-side switches. For smaller output voltages the current limitation is disabled in order to minimise the saturation voltages without increasing the power dissipation. Figures 1 and 2 show the characteristic of the switching channels when activated. Region "A" is the saturation range, where the current limitation is not fully active yet and region "B" is the current limited range. Region "C" corresponds to the free-wheeling circuit activated. The switching channels are designed so that the low-side switches

can only sink current and the high-side switches can only source current (no reverse current).

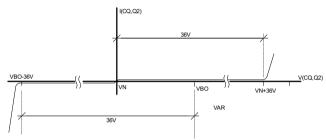

#### Free-wheeling circuit for inductive loads

The free-wheeling circuit is always present and does not depend on the output status. It is activated by voltages higher than 36 V at the low-side switches referenced to VN or lower than -36 V at the high-side switches referenced to VBO. In that case the corresponding channel will switch on without current limitation (see Figure 3).

Figure 3: Free-wheeling characteristic

#### **Dead time**

In order to avoid current flow between high- and lowside switch in push-pull configuration, a dead time  $t_{dead}$ is implemented as shown in Figure 4 (cf. Electrical Characteristics Nos. 112 and 212).

Figure 4: Propagation delay

#### **Excitation current**

With registers EXCx an additional current  $I_{\text{exc}}$  can be activated for driving capacitive loads. Figure 5 shows the characteristic of one channel with the excitation current enabled (cf. Electrical Characteristics Nos. 110, 111, 210 and 211). The excitation current duration is controlled by the TEXCx registers.

| EXC1 | Addr. 0x03; bit 3              | R/W 0 |

|------|--------------------------------|-------|

| 0    | CQ excitation current disabled |       |

| 1    | CQ excitation current enabled  |       |

Table 4: CQ excitation current selection

#### **IO-Link SLAVE TRANSCEIVER**

Rev B2, Page 14/38

| EXC2 | Addr. 0x04; bit 3              | R/W 0 |

|------|--------------------------------|-------|

| 0    | Q2 excitation current disabled |       |

| 1    | Q2 excitation current enabled  |       |

Table 5: Q2 excitation current selection

| TEXC1 | Addr. 0x03; bit 6                     | R/W 0 |

|-------|---------------------------------------|-------|

| 0     | CQ excitation current for typ. 2.5 µs |       |

| 1     | CQ excitation current for typ. 7.5 µs |       |

Table 6: CQ excitation current duration

| TEXC2 | Addr. 0x04; bit 6                     | R/W 0 |

|-------|---------------------------------------|-------|

| 0     | Q2 excitation current for typ. 2.5 µs |       |

| 1     | Q2 excitation current for typ. 7.5 μs |       |

Table 7: Q2 excitation current duration

Figure 5: Excitation current

#### High speed mode

To meet the IO-Link COM3 requirements, the *High Speed* mode has to be enabled (HSPx). This mode increases the output current during communication.

| HSP1 | Addr. 0x03; bit 7           | R/W 0 |

|------|-----------------------------|-------|

| 0    | CQ set to normal speed mode |       |

| 1    | CQ set to high speed mode   |       |

Table 8: CQ High speed mode

| HSP2 | Addr. 0x04; bit 7           | R/W 0 |

|------|-----------------------------|-------|

| 0    | Q2 set to normal speed mode |       |

| 1    | Q2 set to high speed mode   |       |

Table 9: Q2 High speed mode

# Switching converter with spread spectrum oscillator

The switching converter is controlled by VHDIS. The target voltage at VHL is set at VHV(5:0). To reduce the electromagnetic interference generated by the switching converter, a *spread spectrum oscillator* has been introduced. Here the switch is not triggered by a fixed

frequency but by a varying 32-step frequency mix. Generated interference is thus distributed across the frequency spectrum with its amplitude reduced at the same time. This feature can be disabled via RNDDIS.

| RNDDIS | Addr. 0x09; bit (7)                      | R/W 0 |

|--------|------------------------------------------|-------|

| 0      | DC/DC converter noise spreading enabled  |       |

| 1      | DC/DC converter noise spreading disabled |       |

Table 10: DC/DC converter noise spreading

| VHDIS | Addr. 0x09; bit (6)      | R/W 0 |

|-------|--------------------------|-------|

| 0     | DC/DC converter enabled  |       |

| 1     | DC/DC converter disabled |       |

Table 11: DC/DC converter disabling

| VHV(5:0) | Addr. 0x09; bit (5:0) R/W 001011                               |

|----------|----------------------------------------------------------------|

| 0x00     | VH regulated to the min voltage                                |

|          |                                                                |

| 0x04     | VH regulated to 5 V (cf. Electrical Characteristics No.905)    |

|          |                                                                |

| 0x0B     | VH regulated to 6.75 V (cf. Electrical Characteristics No.905) |

|          |                                                                |

| 0x18     | VH regulated to 10 V (cf. Electrical Characteristics No.905)   |

|          |                                                                |

| 0x2C     | VH regulated to 15 V (cf. Electrical Characteristics No.905)   |

|          |                                                                |

| 0x3F     | Not supported                                                  |

Table 12: DC/DC converter output voltage

#### VCC3 regulator

The VCC3 regulator provides a 3.3 V voltage with up to 50 mA when VBR and VH are supplied. The VCC3 regulator supplies the digital circuitry of the chip. VBR and VH must be supplied for VCC3 operation.

#### **VCC** regulator

The VCC regulator is configured at VSET to 1.8, 2.5, 3.3, or 5 V output (cf. Electrical Characteristic No. A01) with up to 50 mA (see Table 13).

| VCC voltage | VSET setting               |

|-------------|----------------------------|

| 1.8 V       | shortcircuited to pin VCC  |

| 2.5 V       | shortcircuited to pin GND  |

| 3.3 V       | shortcircuited to pin VCC3 |

| 5 V         | pin open                   |

Table 13: VSET configuration for VCC regulator

#### **10**-Link SLAVE TRANSCEIVER

Rev B2, Page 15/38

The VSET pin is evaluated during the first 50 ms after power-up. Hence VSET must be stable longer than typ. 150 µs before the VCC regulator is switched to its operating point. After the first 50 ms have elapsed, changes at VSET don't affect the configuration. The configuration is redundantly stored and monitored for integrity to prevent undesired changes due interferences. For the 5 V configuration (VSET pin open), a 100 pF capacitor between VSET and GND is advised for additional filtering in noisy environments. Once the VCCOK status flag is cleared, the regulator is assumed to be correctly configured and its configuration can be read at SETV. VBR and VH must be supplied for VCC operation. The regulator can be disabled via EVCC.

| SETV(1:0) | Addr. 0x00; bit 7:6               | R |

|-----------|-----------------------------------|---|

| 00        | VCC regulator configured to 3.3 V |   |

| 01        | VCC regulator configured to 5 V   |   |

| 10        | VCC regulator configured to 1.8 V |   |

| 11        | VCC regulator configured to 2.5 V |   |

Table 14: SETV status

| EVCC | Addr. 0x06; bit (6)    | R/W 1 |

|------|------------------------|-------|

| 0    | VCC regulator disabled |       |

| 1    | VCC regulator enabled  |       |

Table 15: VCC regulator control

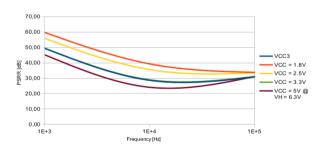

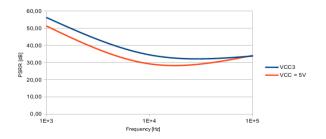

#### Power Supply Rejection Ratio (PSRR)

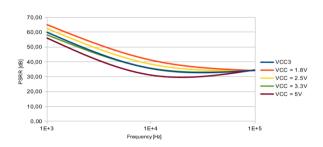

Figures 6 to 8 show the power supply rejection ratio for different VH settings.

Figure 6: PSRR with VH = 4.5 V

Figure 7: PSRR with VH = 8 V

Figure 8: PSRR with VH = 24 V

#### Overload detection

To protect the device from excessive power dissipation due to high currents the switches are clocked, if an overload occurs. If a short circuit is detected, i.e. if the voltage at the switch output overshoots or undershoots *Overload Detection Threshold off* (cf. Electrical Characteristics Nos. 105 and 205), the switches are shut down for typ. 50 ms (cf. Electrical Characteristics No. 302).

The level of power dissipation depends on the current and the time during which this current flows. A current which fails to trigger the overload detection is not critical; high current can also be tolerated for a short period and with low repetition rates. This is particularly important when switching capacitive loads (charge/discharge currents).

There are two overload detection modes. In Normal Overload Detection Mode (SOVL = 0), overload is detected only when the switches are continously overloaded for longer than typical 160  $\mu$ s (cf. Electrical Characteristics No. 301).

| SOVL | Addr. 0x06; bit 6              | R/W 1 |

|------|--------------------------------|-------|

| 0    | Normal overload detection mode |       |

| 1    | Smart overload detection mode  |       |

Table 16: Overload mode configuration

In Smart Overload Detection Mode (SOVL = 1, iC-GF legacy mode) two back-end integrators follow the switches for the purpose of overload detection. Each integrator is a counter which is updated together with the on-chip clock. If an overload is detected at one channel the respective counter is incremented. If no overload is apparent, the counter is decremented after a certain time. This time is controlled by the DTY1(1:0) and DTY2(1:0) for channel CQ and Q2 respectively.

### **IO-**Link SLAVE TRANSCEIVER

Rev B2, Page 16/38

| DTY1(1:0) | Addr. 0x03;        | bit (5:4) | R/W 10 |

|-----------|--------------------|-----------|--------|

| 00        | Duty cycle of 1:4  |           |        |

| 01        | Duty cycle of 1:8  |           |        |

| 10        | Duty cycle of 1:10 |           |        |

| 11        | Duty cycle of 1:15 |           |        |

Table 17: Overload detection duty cycle for CQ

| DTY2(1:0) | Addr. 0x04; bit (5:4) | R/W 10 |

|-----------|-----------------------|--------|

| 00        | Duty cycle of 1:4     |        |

| 01        | Duty cycle of 1:8     |        |

| 10        | Duty cycle of 1:10    |        |

| 11        | Duty cycle of 1:15    |        |

Table 18: Overload detection duty cycle for Q2

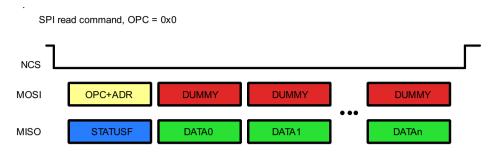

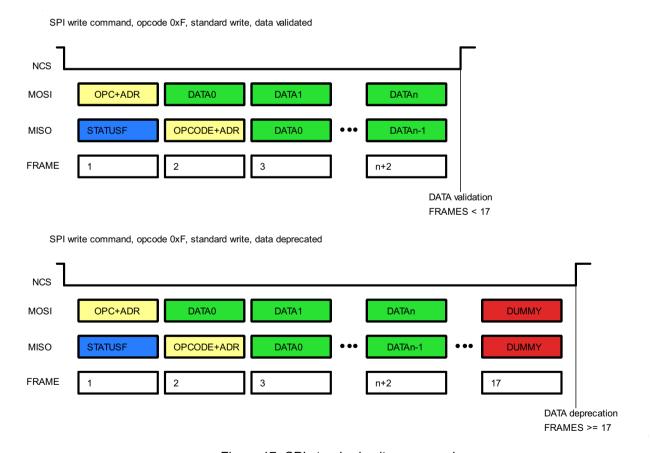

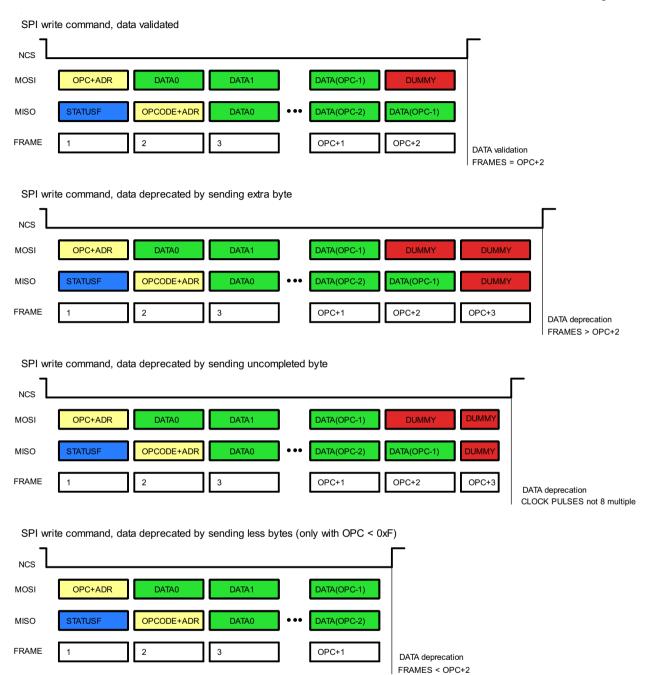

When the counter reaches the overload level, the corresponding output switch is shut down for typical 50 ms which is signaled by clearing NOVL1, NOVL2. This will